Free Download Altair PollEx 2023.0 | 706.3 mbOwner:

Free Download Altair PollEx 2023.0 | 706.3 mbOwner:Altair

Product Name:PollEx

Version:2023.3 with PDF Documentation

Supported Architectures:x64

Website Home Page :www.altair.com

Languages Supported:multilanguage

System Requirements:Windows *

Size:706.3 mb

The Altair development team is pleased to announce the availability of

PollEx 2023.0is a PCB-level Electronic Design Automation (EDA) software suite covering design review, analysis and manufacturing.

Highlights

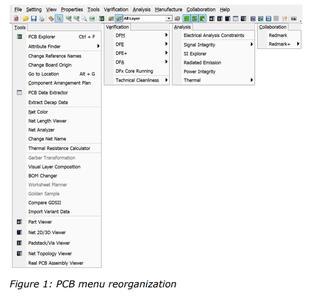

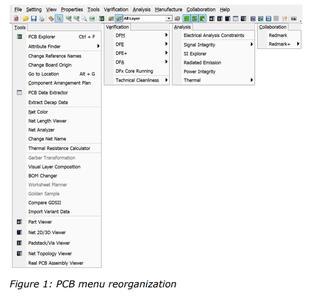

- The PCB menus have been reorganized to provide better clarity

- The Technical Cleanliness feature has been enhanced to export analysis results to ODB++ format.

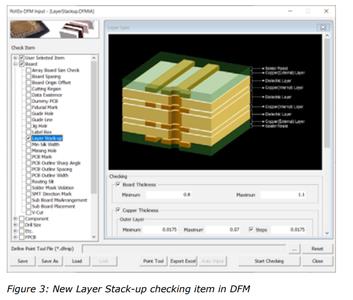

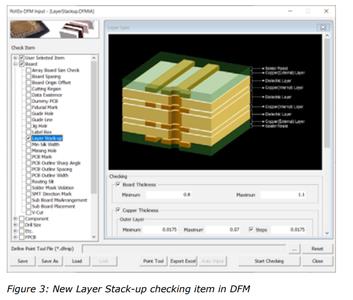

- The Board category in DFM now has a new Layer Stack-up checking item.

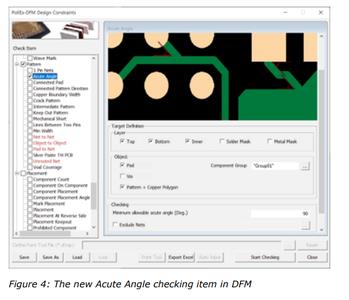

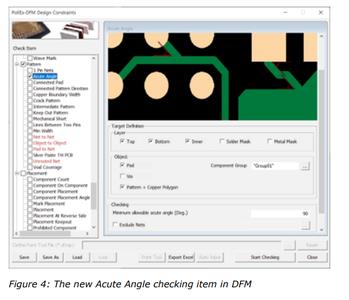

- The Pattern category in DFM now has a new Acute Angle checking item.

- A new SerDes simulation feature has now been added to Network Analysis for single or differential lines. This feature verifies the Bathtub and Statistical eye diagrams for the IBIS-AMI-based SerDes models in SI. A SerDes system simulation involves a transmitter (Tx) and a receiver (Rx) connected by a passive analog channel. You can perform statistical analysis and time-domain analysis. This function will enable you to quickly and accurately analyze the SerDes full channel composed of PCB, Connector, and Cable.

- A new feature to enable automatic setup of pin mapping using Excel has now been added to the package S-Parameter model in SI. After extracting the S-Parameter of the package using Network Analysis, you can perform Signal Integrity Analysis of the entire flow of DIE + Package + PCB more easily by connecting it to the simulation model. However, to extract the S-Parameter Model of the Lead Wire of the package, use other 3D tools.

- The IR Drop engine has now been enhanced to mesh 'trace-type net' which improves accuracy in PI. Since the mesh trace requires more analysis time, you can select the mesh type and review the Current Density in the trace-type object based on your requirements.

New Features

PollEx Modeler

PCB

- The PCB menus have been reorganized to provide better clarity.

PollEx Verification

DFM

- Added a new checking item of the Layer Stack-up in the Board category.

- Added a new checking item of the Acute Angle in the Pattern category.

DFE+

- A new Dynamic ODT option has now been added to the Timing Margin and Timing Skew features. This option enables you to assign a different type of termination for each load under multi-load conditions.

Technical Cleanliness

- Two additional measure base options such as Pad and Solder Mask have now been added.

- An additional option to ignore regions in the Constraint tab components has now been added.

- A new Technical Cleanliness feature has now been enhanced to export analysis results to ODB ++ format.

PollEx Interface from ECAD

Mentor Graphics Xpedition

- The Siemens Xpedition importer has now been added directly from its binary data using the API.

PollEx Analysis

SI

- The SerDes simulation in the Network Analysis, specifically for single lines or differential lines has now been added. It verifies the Bathtub and Statistical eye diagrams for the IBIS�AMI-based SerDes models.

- The Network Parameter of the selected VIAs in the Net Topology Analyzer is added. This enables to extract S/Y/Z parameters, impedance, and equivalent RLGC values between VIAs' in/out ports.

PI

- Added the IR Drop 2 engine to select the meshing type of Polygon with trace.

Enhancements

PollEx Modeler

PCB

- The layer setting of the Visual Layer Composition has now been enhanced.

- You can now work on multiple designs without closing opened designed data.

- Modified to display silk on/off in the Real PCB Assembly Viewer.

CP

- The search feature is now enhanced in a user information setting.

UPE

- To include a component flag pin name and packing information is now enhanced to export Mount Information to a CSV file.

PollEx Verification

DFM

- An option in the BGA item is added to prohibit PTH vias between BGA pads.

- An option to check a number of connected patterns is added to the BGA pad in the BGA item.

- An option is added in the BGA item to check if all patterns connected to the BGA pads have the same thickness.

- Added an option in the Component Spacing 2 item to check the maximum distance between Solder Mask and Pad in the same component.

- Added an option to check if patterns connected to pads with length-width asymmetry are connected through the shorter side in the Connected Pattern Direction item.

- Added an option to check the Tie leg width and length in the Copper Connected Pad item.

- Added an option to check the clearance between the coverlay open area and copper in the Coverlay item.

- Added an option in the Crack Pattern item on whether teardrops are designed on the target component's pads

- Added an option in the Cutting Region item to recognize only the patterns crossing the PCB outline as JTAG patterns.

- Added an option to check missing pads on all layers of DIP-type holes in the Dip Annular Ring item.

- Added an option to check the existence of S/R covered copper between the Pad edge and exposed pad for specified components like QFN, SON, and DFN in the Edge Pin Size item.

- Added an option in the Hole Distance item to check the clearance between holes and components.

- Added an option to check whether the via hole is located on the component pad's central axis (long axis) in the Hole Through Pad item.

- Added a new check item for the PCB board thickness in the Layer Spec item.

- Added a measure base type of COC+Pad/Solder Mask Overlap in the PCB Outline Spacing item.

- Added an option in the PCB Outline Spacing item to check the clearance for the figure objects.

- Added an option in the Ref Name Silk item to check the clearance between components and reference names.

- Added an option to check the existence of a solder mask between the thermal pad and I/O pad in the Solder Resist Pad item.

- Added an option in the Solder Resist Pad item to check the maximum distance between Solder Mask and Pad in the same component.

- An option to recognize as different nets if other nets are connected to the same reference has been added in the Solder Resist Pad item.

- An option to check the teardrop length has been added in the Teardrop item.

- A BGA measure base in the Underfill item has been added.

- Added an option to verify the maximum number of layers of Laser/Buried/Blind vias that can penetrate in the Via Overstack item.

- An option in the Underfill item has been added to check the clearance between BGA and Via/ NPTH/Test Point.

- Enhanced the Link to ECAD feature with the Xpedition to navigate the correct layer.

DFE+

- Enhanced a feature to consider Coplanar structure in the Impedance item.

- The Impedance Map has been enhanced to display a ZCommon impedance.

- Enhanced to display the net name and impedance value of the current cursor position in the Impedance Map.

Technical Cleanliness

- The unit notation for the results report is added.

- The flow to save when the input parameter changes has been enhanced.

PollEx Analysis

SI

- A new feature to enable automatic setup of pin mapping using Excel has been enhanced to the package S-Parameter model in SI.

- Generated Multiple Models in the Transmission Line Analysis has been enhanced to generate differential line models automatically.

- Enhanced to analyze multiple nets in the Net Topology Analyzer of the Network Analysis. Please note that the coupling effect should be analyzed with the Crosstalk analysis.

PI

- An option to set prohibited areas for Decap placement in the PDN analysis has been added.

- Enhanced the IR Drop engine to mesh trace type net to improve accuracy.

- The VRM and PORT selection is enhanced to modify the target pin in the PI Analyzer.

- Enhanced to support mil unit in the DC IR Drop and AC PDN analysis.

- Modified the IR-Drop analysis to select a port between PIN and Die.

- The marker feature is modified to display the trace correctly in the IR Drop analysis.

PollEx Interface from ECAD

Cadence Allegro

- Enhanced the zoom factor when crossprobing with DFx results in the Link to ECAD feature.

IPC-2581

- The importer to import the material information has been enhanced.

Resolved Issues

- The missing build-up VIA pads in the Cadence Allegro importer issue has been fixed.

- A bug in the silk screen text location on the Cadence Allegro importer has been fixed.

- Fixed parse error in the CADVANCE importer.

- The missing particular Artwork layers in the Mentor Board Station importer issue has been fixed.

- The misplaced component pads in the ODB++ importer issue has been fixed.

- Fixed a bug with incorrect arc direction in the DXF exporter.

- The Auto Naming option on the DFx Core Running bug has been fixed.

- Incorrect grouping of Sub-Items in the Result Table of Copper Cross Over Item in DFE issue has been fixed. The same option was displayed in duplicate in several Sub-Items.

- An issue for not recognizing holes declared as Components in the Power Net to Net item of DFE has been fixed.

- An issue that a single-ended net is displayed in the differential net category when displaying impedance check results in the DFE+ is resolved.

- Fixed an issue to open the Net Topology Analyzer of the Network Analysis in the SI after assigning the Package S-Parameter.

- An issue where Crosstalk Analysis could not be performed when a space was included in the VIA name has been fixed.

- Resolved an issue that the IBIS model existing in the Part Directory is not assigned when executing the Properties/Part menu.

- An issue that analysis is not possible when the passive component is directly connected to the plane without trace during the IR-Drop Analysis has been solved

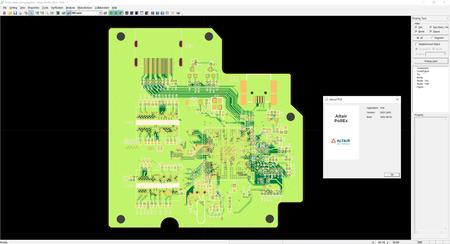

Altair PollExis the most comprehensive and integrated set of PCB design viewing, analysis and verification tools. It provides powerful rule-based checking tools (DFM, DFA and DFE) to detect faults early in design and also provides easy solution for SI and thermal analysis of PCBs using the integrated parts and material libraries. PollEx is not just a printed circuit board (PCB) verification tool, it is solution that accelerates the development of today's smart, connected, and tightly packaged electronic products. It is used by global industry leaders to improve efficiency, increase performance, enable teamwork, and enhance collaboration. Altair offers tools for full system analysis that integrate mechanical, thermal, electromagnetic, and embedded code design flow with PCB design.

Altair PollEx - Advanced Capabilities Overview

Altair PollEx is the most comprehensive and integrated set of PCB design review and verification tools in the market for electrical, electronics and manufacturing engineers. PollEx Advanced Tools includes PollEx PCB Verification (DFM, DFA, DFE, DFE+ and Logic DFE), Solver (SI, PI and Thermal), MFGs (Mounting Emulator, Metal Mask Manager, Soldering Amount Calculator and etc.) and PollEx PCB UPE (Unified Part Editor).

Altairis a global technology company that provides software and cloud solutions in the areas of product development, high performance computing (HPC) and data analytics. Altair enables organizations across broad industry segments to compete more effectively in a connected world while creating a more sustainable future.

Buy Premium From My Links To Get Resumable Support,Max Speed & Support Me

Altair PollEx 2023.0 with PDF Documentation (x64) Torrent Download , Altair PollEx 2023.0 with PDF Documentation (x64) Crack Download , Altair PollEx 2023.0 with PDF Documentation (x64) Patch Download , Altair PollEx 2023.0 with PDF Documentation (x64) Serial Keygen Download

Comments